# VLSI Design Tsung-Chu Huang Department of Electronic Engineering National Changhua University of Education Email: tch@cc.ncue.edu.tw

2011/09/19

-C. Huang, NCUE Fall 2011

# **Brief Syllabus**

- 1. Visit <u>http://testlab.ncue.edu.tw/tch</u> for details

- 2. Reference: Weste & Harris's textbook

- 3. All-English Instruction

- 4. Requirements for This Course:

- ✓ Basic Logic Design

- ✓ Hardware Descriptive Language

- ✓ Self-Motivation

- 5. Addendum:

- ✓ ftp://testlab.ncue.edu.tw/VLSI

C.-C. Huang, NCUE Fall 2011

# **Course Scope**

1. Scoped in CMOS with 80% Digital + 20% Else

#### 2. Why Go CMOS:

- 1. Low power/cost

- 2. High density

- 3. High Noise Margin

- 4. High Regularization

- 5. Ratioless Circuits

- 6. Compromised for Analog Design

- 7. Highly Developed.

#### 3. Why Digital First:

1. High digitalization except AD/DA and a part of PLL

2. Easy to start up

## **Major Contents**

Page

Page

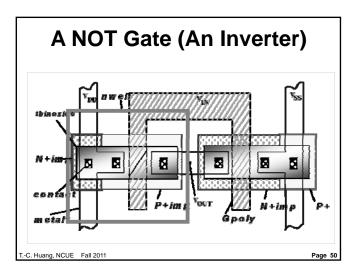

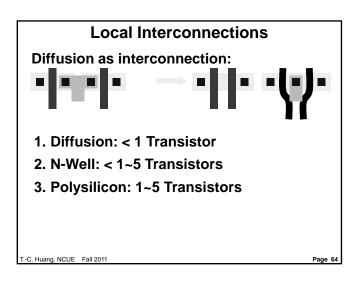

- 1. Logic-Oriented MOS Theory Transistor Sizing

- 2. Logic Cells Full-custom Layout

- 3. Digital IC Synthesis Cell-base Layout

- 4. Logic Structures and RTL Modules

- 5. Introduction to Digital IP

- 6. Introduction to Memory Design

- 7. Introduction to Logic Testing

- 8. Introduction to Some Basics for Analog Circuits

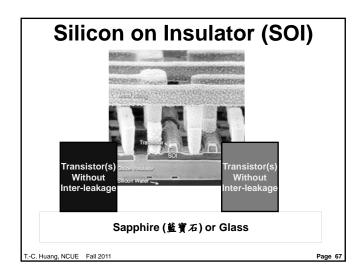

- 9. Introduction to SOC Design

.-C. Huang, NCUE Fall 2011

# **Today's Outline**

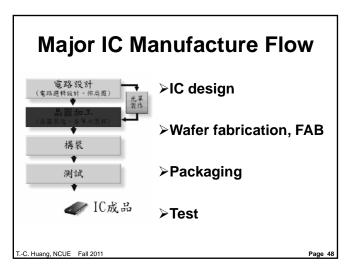

- Chips Everywhere! How do they come from?

- The IC Design Service in Taiwan, CIC

- Introduction to TSMC, the largest foundry

- Other FABs over the world

- Process Technology

- Context Extracted from the above videos

- > Animation in the view of Layout Engineers

- Tapin Flow via CIC

- Homework #1 Given and due to 10/3.

.-C. Huang, NCUE Fall 2011

Page 5

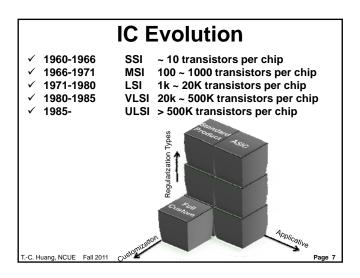

# **IC Evolution**

- ✓ 1947 First Transistor (Shockley, Bardeen and Bratain)

- ✓ 1958 TI Monolithic IC

- 1959 Fairchild & TI Planar silicon IC

- ✓ 1961 Fairchild & TI Commercial monolithic IC (RTL)

- ✓ 1962 TI Diode-transistor logic (DTL)

- ✓ 1962 Sylvania Transistor-transistor logic (TTL)

✓ 1962 Motorola Emitter-coupled logic (ECL)

- ✓ 1962 Motorola Emitter-coupled

✓ 1962 RCA & Fairchild MOS IC

- 1962 RCA & Pair Child MOSTC

1963 RCA Complementary MOS (CMOS)

- ✓ 1964 Fairchild First linear IC

- ✓ 1968 Intel MOS memory chips

- ✓ 1969 Bell Labs Charge-coupled devices (CCD)

- ✓ 1970 Mostek MOS calculator chips

- ✓ 1971 Intel Microprocessor

- ✓ 1972 IBM & Philips Integrated Injection logic

T.-C. Huang, NCUE Fall 2011

T.-C. Huang, NCUE Fall 2011 Refer to <u>http://poli.cs.vsb.cz/edu/arp</u>/down/vyroba-cpu/vyrob

# Photo Resist Application Intel®01

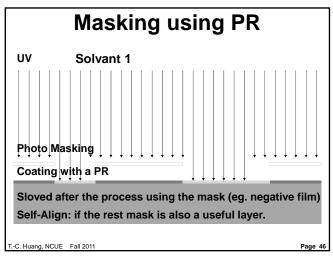

- > The blue liquid is a photo resist (PR) finish similar to those used in film for photography.

- > The wafer spins during this step to allow an evenlydistributed coating that's smooth and also very thin.

- > The photograph is analogy to traditional lithography.

Huang, NCUE Fall 2011 Refer to http://poli.cs.vsb.cz/edu/arp/down/vyroba-cpu/vyroba-cpu.html Page

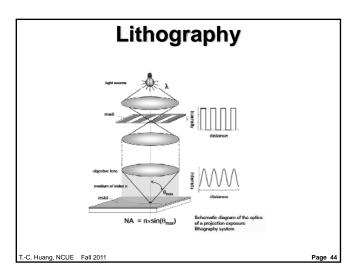

- versa. Using masks that act like stencils creating various circuit patterns.

- > A lens reduces the mask's image to a small focal point.

- > The resulting "print" on the wafer is typically 4X smaller, than the mask's pattern.

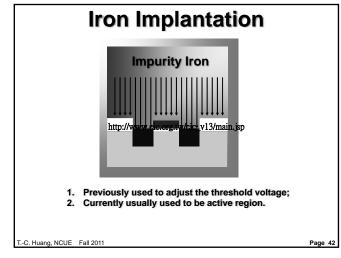

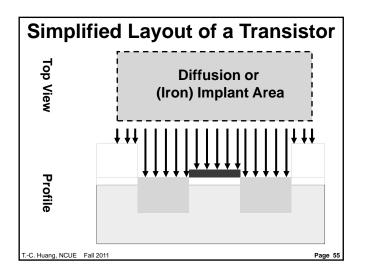

#### Intel®01 Intel®01 Iron Implantation Wafer Electroplating The exposed areas of the silicon wafer are bombarded > The wafers are put into a copper sulphate solution at with ions. this stage. > lons are implanted in the > Copper ions are deposited onto the transistor through a process called electroplating. silicon wafer to alter the > The copper ions travel from way silicon in these areas the positive terminal (anode) conduct electricity. to the negative terminal (cathode) Ions are propelled onto the which is represented by the wafer. surface of the wafer at > Then the copper ions settle as very high velocities a thin layer on the wafer surface. ~ 10<sup>5</sup>m/s. C. Huang, NCUE Fall 2011 Refer to http://poli.cs.vsb.cz/edu/arp/down/vyroba-cpu/vyroba-cpu.html .-C. Huang, NCUE Fall 2011 Refer to http://poli.cs.vsb.cz/edu/arp/down/vyroba-cpu/vyroba-cpu/

#### Intel®01 Final Test: CPU Testing > During final test the processors are tested for their key characteristics, usually the tested characteristics are

power dissipation and maximum frequency.

C. Huang, NCUE Fall 2011 Refer to http://poli.cs.vsb.cz/edu/arp/down/vyroba-cpu/vyroba-cpu.html

and batches are divided and sold according to stable specifications.

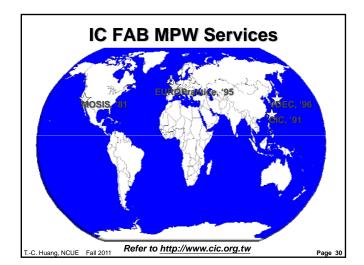

### Some Terminology > FAB: fabrication, analogy to layout-style manufacture > Foundry: factory for basing the industry chain like the metal castings, especially for semiconductor industry FABless Design House: small design company usually w/o FAB equipments > CIC: Chip Implementation Center, National Applied **Research Laboratories** MPW: Multi-Project Wafer .-C. Huang, NCUE Fall 2011 Page 29

## Videos on Silicon Wafer Processing

- Wafer Process at Texas Instrument, 2000 (9 min)

- Semiconductor Technology at TSMC, 2011 (8 min)

- Chip Manufacture Process, 2008 (10min)

- > CPU Manufacture at AMD, 2009 (11min)

Context Reviews on Process Tech

1. Si Semiconductor Technology

2. Basic CMOS Technology

3. CMOS Process

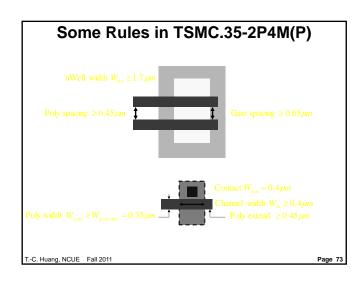

- 4. Layout Design Rules

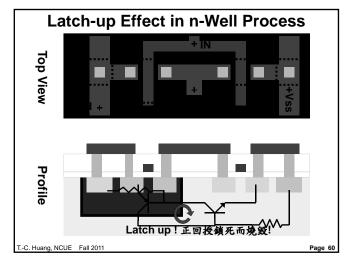

- 5. Latchup Effect

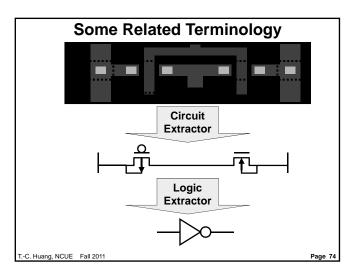

- 6. Extractor & DRC

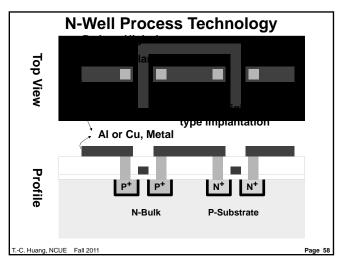

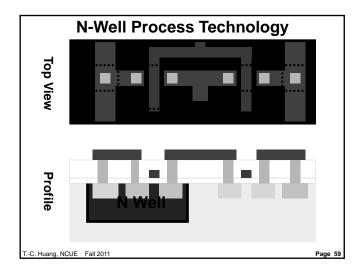

- 7. An n-Well CMOS Process Flow

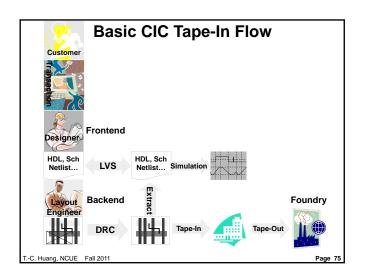

- 8. CIC Tape-In Flow & Tutorial

T.-C. Huang, NCUE Fall 2011

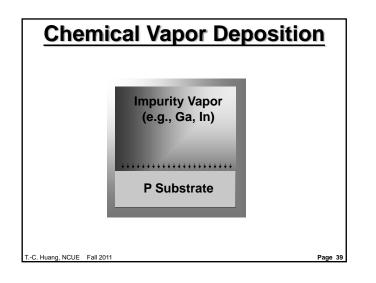

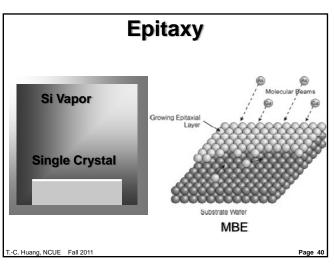

- 2.Epitaxy (磊晶)

- 3.Deposition (沉積)

- 4.Implantation (植入)

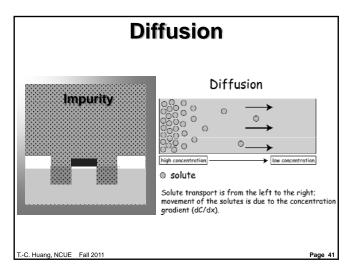

- 5.Diffusion (擴散)

T.-C. Huang, NCUE Fall 2011

T.-C. Huang, NCUE Fall 2011

# Wafer Treatments

- 1. Grinding delete coarse surface by crushing

- 2. Slicing separate to wafers

- 3. Lapping flatten by press

- 4. Etching delete by dissolving

- 5. Polishing flatten fine as a mirror

- 6. Cleaning

- 7. Inspection probably by peer eyes

T.-C. Huang, NCUE Fall 2011

age 3

Page 32

Page 51

T.-C. Huang, NCUE Fall 2011

#### **Preventing Latch-up**

- 1. Using Twin-Well

- 2. Evolved in DRC

- Connect N/P-well to Vdd/Vss

- Contacts closer to Source-gate

- More contacts for more transistors

- Sometimes one well contact for a transistor.

Page 61

.-C. Huang, NCUE Fall 2011

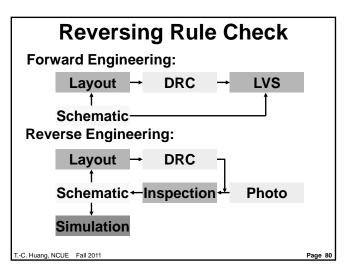

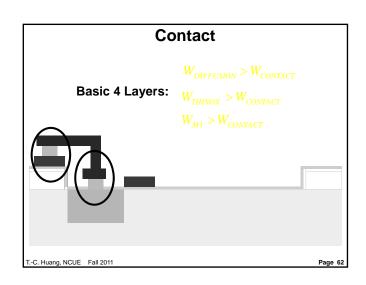

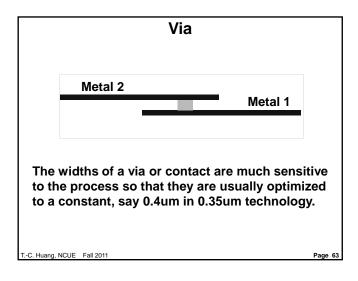

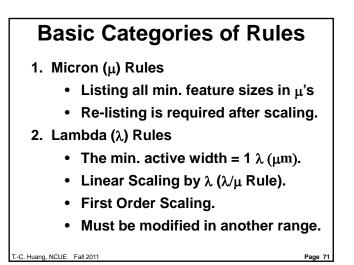

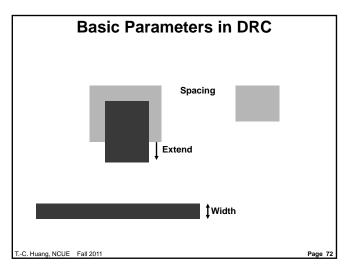

# Design Rule Check (DRC)

- 1. Geometrical

- X-Y Plane: Single-Layer Layout

- Z Plane: Interactions btw Layers

Page 68

2. ERC

T.-C. Huang, NCUE Fall 2011

- Electrical Rule Check

- 3. Custom Rules

## Reverse Engineering (RE) 1. Category • Mechanism • Software: database, programming • VLSI: layout 2. Purpose: • Failure inspection • Amoral hack, referring

• Illegal stealing (duplication)

T.-C. Huang, NCUE Fall 2011

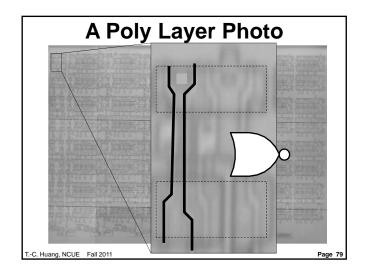

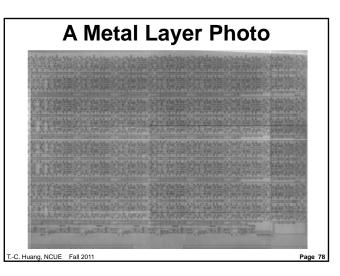

# VLSI RE Flow

- 1. Unpacking

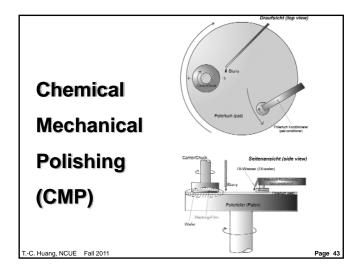

- 2. Chemical Metal Polishing (CMP)

- 3. Photographing

- 4. Inspection

- 5. Schematic

- 6. Simulation & Verification

.-C. Huang, NCUE Fall 2011

Page 77

Page 76