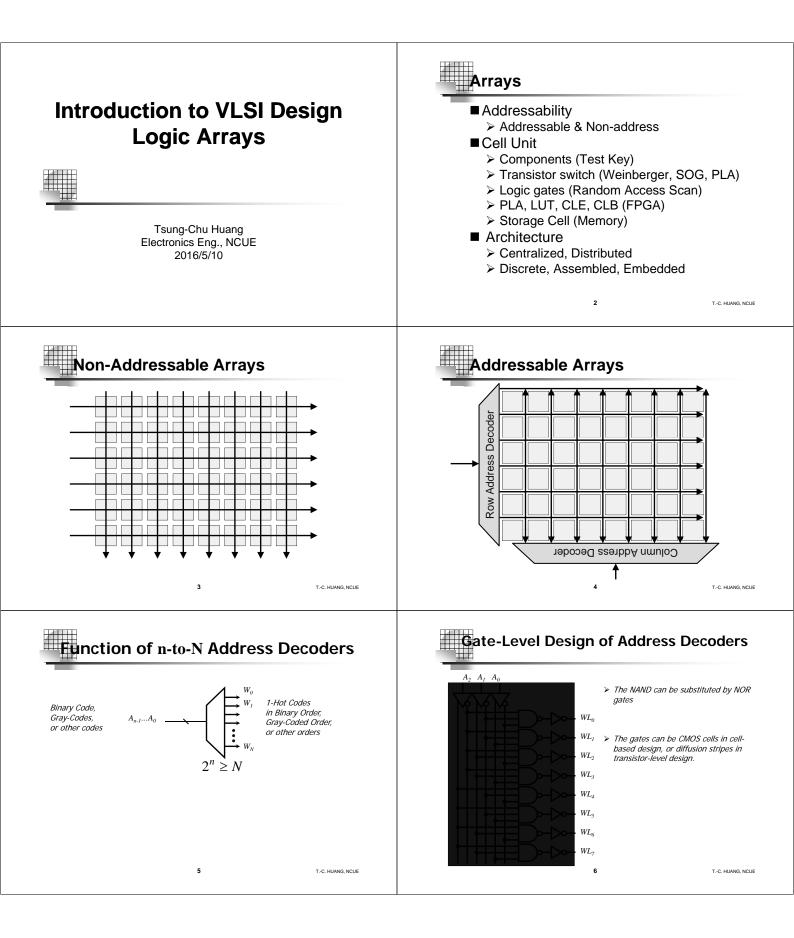

## Computer-aided Design

- Can't design FPGAs by hand >way too much logic to manage, hard to make

- changes Hardware description languages

- > specify functionality of logic at a high level

- Validation high-level simulation to catch specification errors

- >verify pin-outs and connections to other system components

- >low-level to verify mapping and check performance

- Logic synthesis

- >process of compiling HDL program into logic gates and flip-flops T.-C. HUANG, NCUE 43

# Xilinx CAD Tools

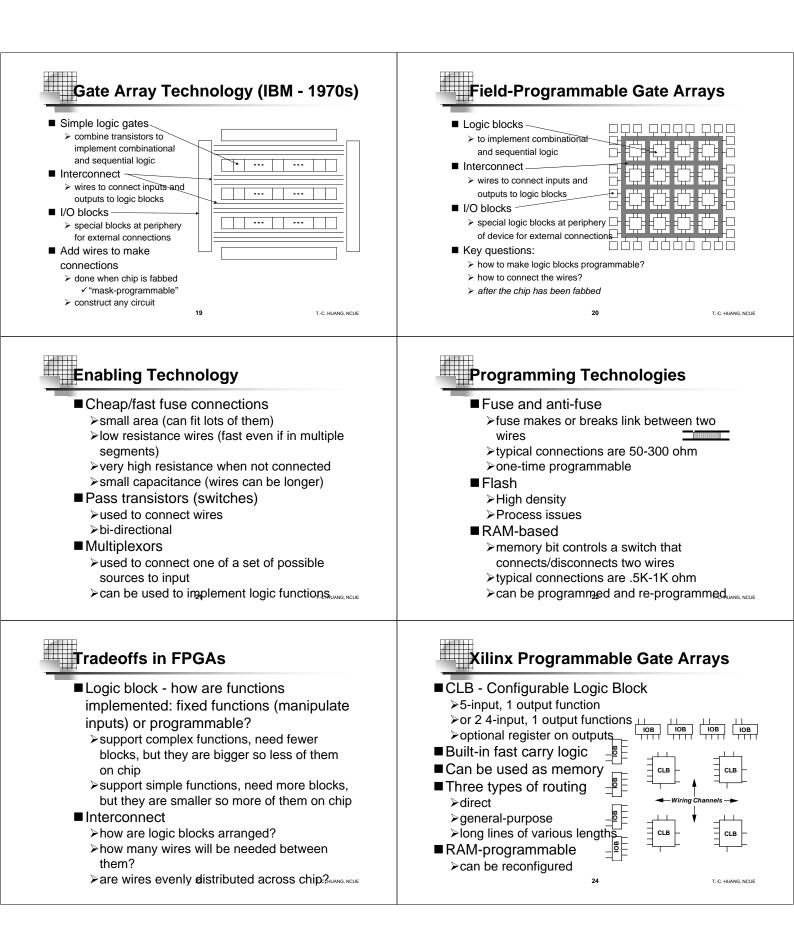

- Verilog/VHDL used to specify logic at Hi-level Combine with schematics, library components

- Synplicity

- ➤ compiles Verilog to logic

- >maps logic to the FPGA cells

- ➢optimizes logic

- Xilinx APR automatic place and route (simulated annealing) >provides controllability through constraints

- ➤handles global signals

- Xilinx Xdelay

- measure delay properties of mapping and aid Xilinx XACT

- >design editor to view final mapping results

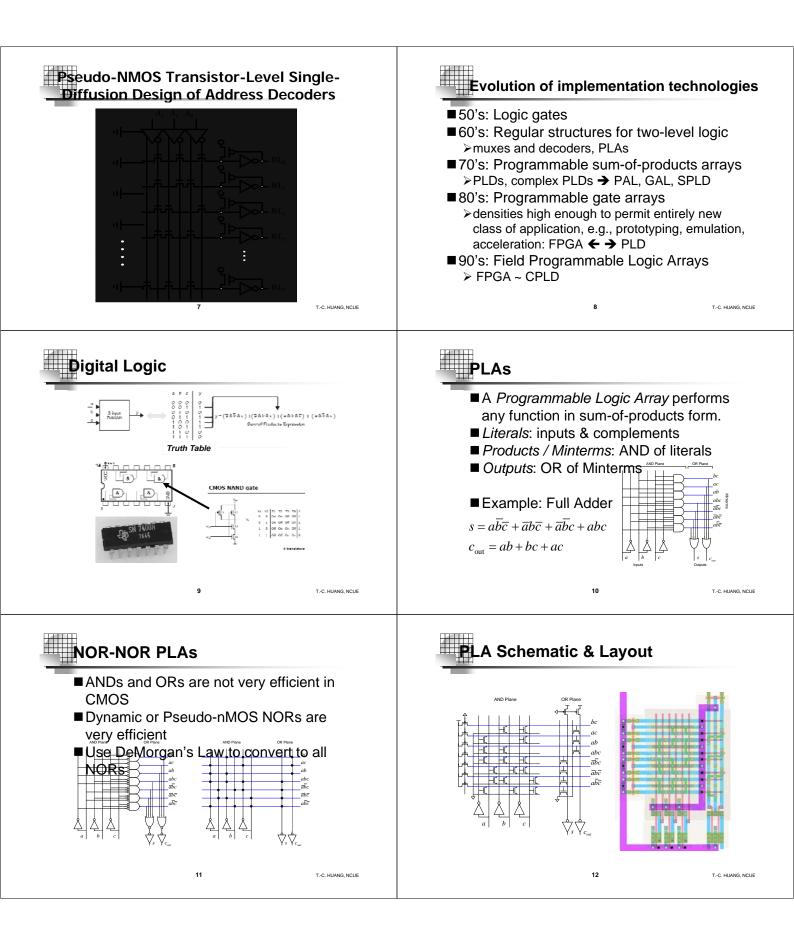

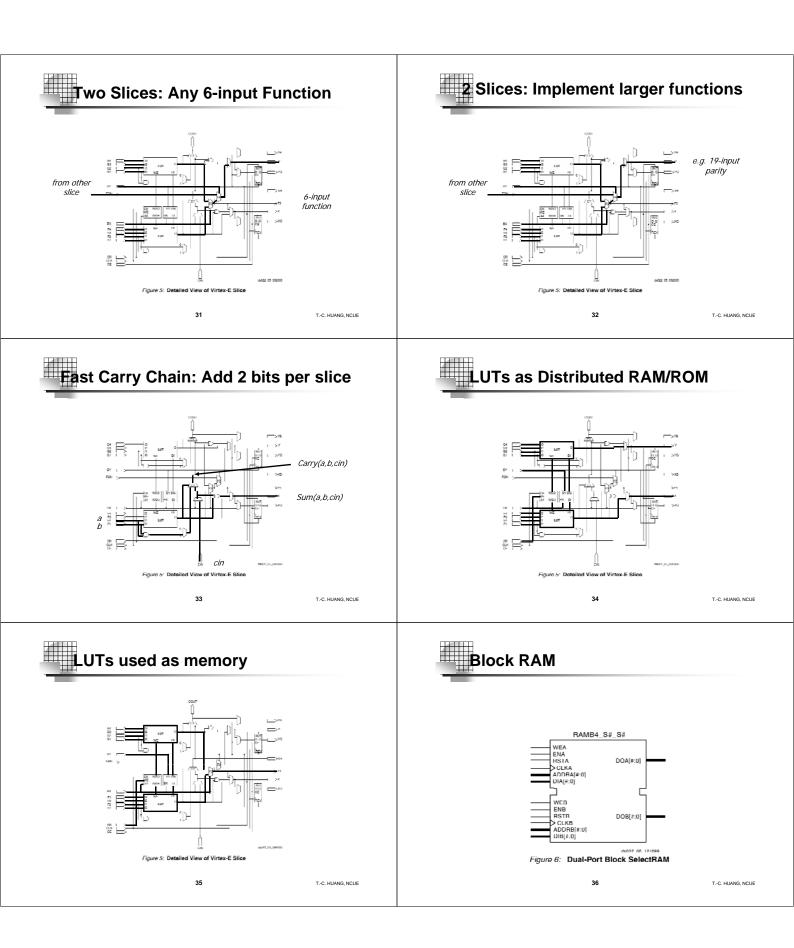

### Applications of FPGAs

- Implementation of random logic

- > easier changes at system-level (one device is modified)

> can eliminate need for full-custom chips

- Prototyping

➤ ensemble of gate arrays used to emulate a circuit to be manufactured

- > get more/better/faster debugging done than possible with šimulation

- Reconfigurable hardware > one hardware block used to implement more than one function

- functions must be mutually-exclusive in time > can greatly reduce cost while enhancing flexibility

> RAM-based only option

Special-purpose computation engines

- hardware dedicated to solving one problem (or class of problems)

- > accelerators attached to general-purpose computers 47

T.-C. HUANG, NCUE

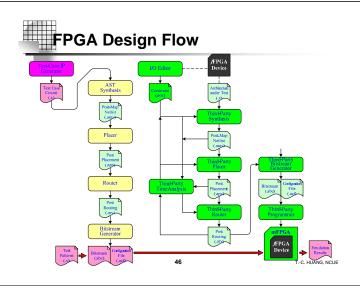

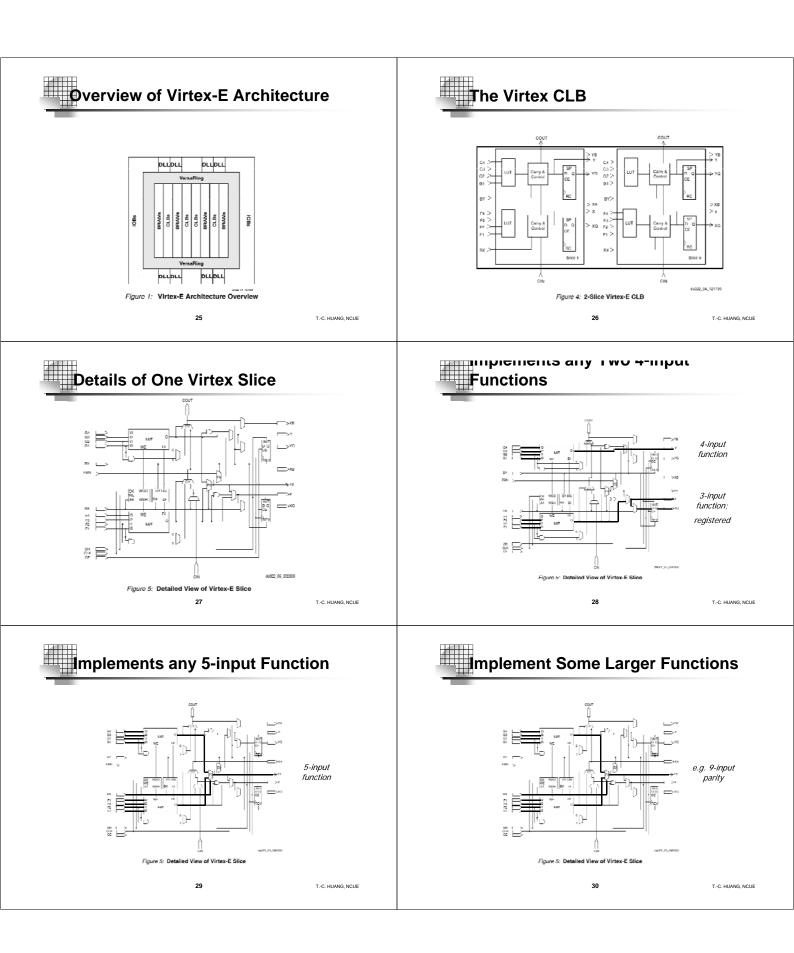

## CAD Tool Path (cont'd)

- Placement and routing ➤assign logic blocks to functions >make wiring connections

- Timing analysis verify paths >determine delays as routed look at critical paths and ways to improve

- Partitioning and constraining >if design does not fit or is unroutable as placed split into multiple chips

- >if design it too slow prioritize critical paths, fix placement of cells, etc.

- > few tools to help with these tasks exist today

- Generate programming files bits to be loaded